- 您现在的位置:买卖IC网 > Sheet目录324 > EK-V6-ML631-G-J (Xilinx Inc)VIRTEX-6 HXT FPGA ML631 EVAL KIT

�� �

�

�

�Virtex-6� FPGA� Data� Sheet:� DC� and� Switching� Characteristics�

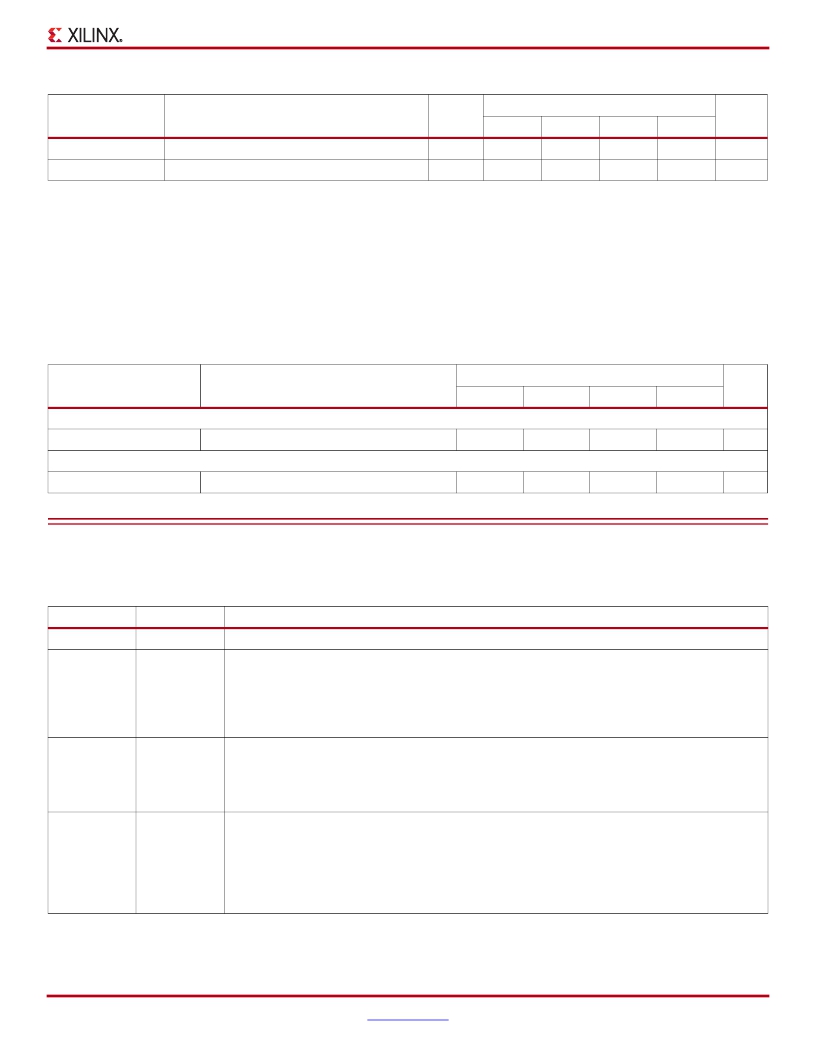

�Table� 73:� Sample� Window�

�Symbol�

�Description�

�Device�

�-3�

�Speed� Grade�

�-2� -1�

�-1L�

�Units�

�T� SAMP�

�Sampling� Error� at� Receiver� Pins� (1)�

�All�

�510�

�560�

�610�

�670�

�ps�

�T� SAMP_BUFIO�

�Sampling� Error� at� Receiver� Pins� using�

�BUFIO� (2)�

�All�

�300�

�350�

�400�

�440�

�ps�

�Notes:�

�1.�

�2.�

�This� parameter� indicates� the� total� sampling� error� of� Virtex-6� FPGA� DDR� input� registers,� measured� across� voltage,� temperature,� and�

�process.� The� characterization� methodology� uses� the� MMCM� to� capture� the� DDR� input� registers’� edges� of� operation.� These� measurements�

�include:�

�-� CLK0� MMCM� jitter�

�-� MMCM� accuracy� (phase� offset)�

�-� MMCM� phase� shift� resolution�

�These� measurements� do� not� include� package� or� clock� tree� skew.�

�This� parameter� indicates� the� total� sampling� error� of� Virtex-6� FPGA� DDR� input� registers,� measured� across� voltage,� temperature,� and�

�process.� The� characterization� methodology� uses� the� BUFIO� clock� network� and� IODELAY� to� capture� the� DDR� input� registers’� edges� of�

�operation.� These� measurements� do� not� include� package� or� clock� tree� skew.�

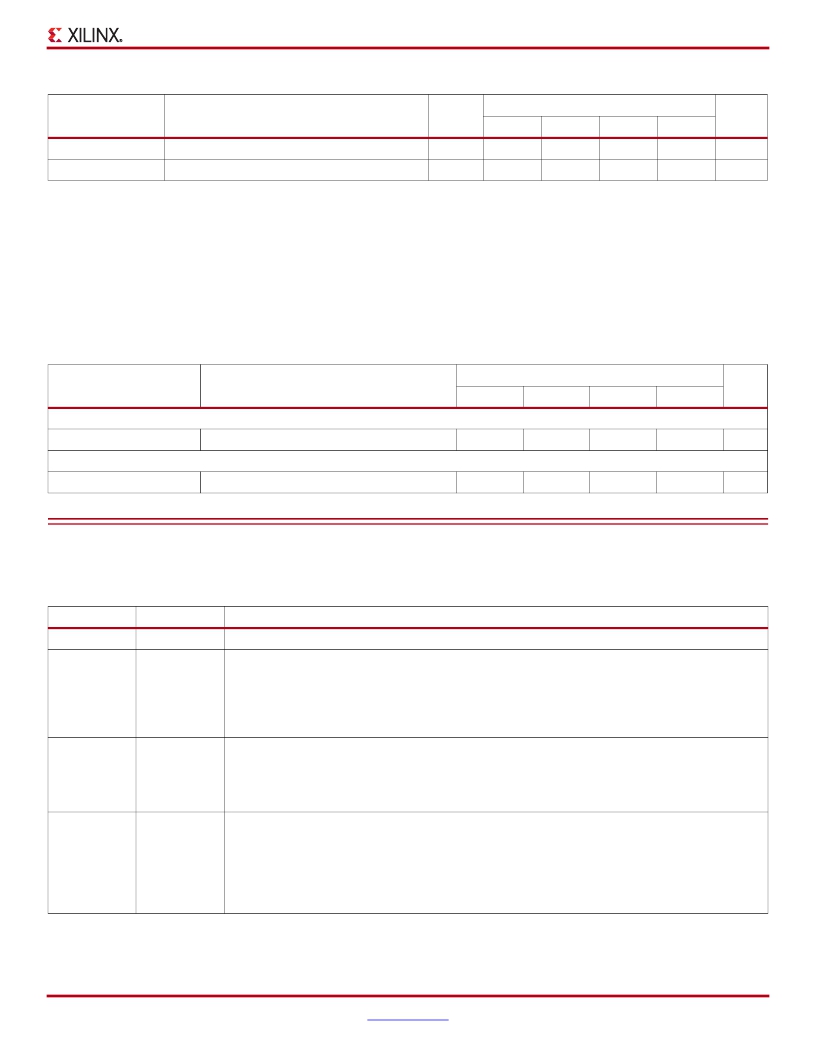

�Table� 74:� Pin-to-Pin� Setup/Hold� and� Clock-to-Out�

�Symbol�

�Description�

�-3�

�Speed� Grade�

�-2� -1�

�-1L�

�Units�

�Data� Input� Setup� and� Hold� Times� Relative� to� a� Forwarded� Clock� Input� Pin� Using� BUFIO�

�T� PSCS� /T� PHCS�

�Setup/Hold� of� I/O� clock�

�–0.28/1.09� –0.28/1.16� –0.28/1.33� –0.18/1.79�

�ns�

�Pin-to-Pin� Clock-to-Out� Using� BUFIO�

�T� ICKOFCS�

�Clock-to-Out� of� I/O� clock�

�4.22�

�4.59�

�5.22�

�5.63�

�ns�

�Revision� History�

�The� following� table� shows� the� revision� history� for� this� document:�

�Date�

�06/24/2009�

�07/16/2009�

�08/19/2009�

�09/16/2009�

�Version�

�1.0�

�1.1�

�1.2�

�2.0�

�Description� of� Revisions�

�Initial� Xilinx� release.�

�Revised� the� maximum� V� CCAUX� and� V� IN� numbers� in� Table� 2,� page� 2� .� Removed� empty� column� from�

�Table� 3,� page� 3� .� Revised� specifications� on� Table� 20,� page� 13� .� Updated� Table� 38,� page� 22� and� added�

�notes� 1� and� 2.� Revised� T� DLYCCO_RDY� ,� T� IDELAYCTRL_RPW� ,� and� T� IDELAYPAT_JIT� in� Table� 53,� page� 41� .�

�Updated� Table� 58,� page� 46� to� more� closely� match� the� DSP48E1� speed� specifications.� Updated�

�T� TAPTCK� /T� TCKTAP� in� Table� 59,� page� 49� .� Updated� XC6VLX130T� parameters� in� Table� 68� through�

��Added� values� for� -1L� voltages� and� speed� grade� in� all� pertinent� tables.� Added� V� FS� and� notes� to� Table� 1�

�and� Table� 2� .� Removed� DV� PPIN� from� the� example� in� Figure� 2� .� Added� networking� applications� to�

�Table� 41,� page� 25� .� Changed� and� added� to� the� block� RAM� F� MAX� section� in� Table� 57,� page� 44� including�

�removing� Note� 12.� Changed� F� PFDMAX� values� and� corrected� units� for� T� STATPHAOFFSET� and� T� OUTDUTY�

��Added� Virtex-6� HXT� devices� to� entire� document� including� GTH� Transceiver� Specifications� .� Updated�

�speed� specifications� as� described� in� Switching� Characteristics� ,� includes� changes� in� Table� 51� ,�

�Table� 57� ,� Table� 58� ,� and� Table� 66� through� Table� 70� .� Comprehensive� changes� to� Table� 14� ,� Table� 15� ,� and�

�Table� 16� .� Added� conditions� to� D� VPPOUT� and� revised� description� of� T� OSKEW� in� Table� 17� .� Removed� V� ISE�

�specification� and� note� from� Table� 18� .� Added� note� 3� to� Table� 23� .� Updated� note� 3� in� Table� 24� .� Updated�

�LVCMOS25� delays� in� Table� 44� .� Updated� specification� for� T� IOTPHZ� in� Table� 46� .� Removed� T� BUFHSKEW�

�from� Table� 71,� page� 60� and� added� values� for� T� BUFIOSKEW� .� Added� values� in� Table� 74� .�

�DS152� (v3.6)� March� 18,� 2014�

�Product� Specification�

��62�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EK-V7-VC707-CES-G

VIRTEX-7 VC707 EVAL KIT

EK-Z7-ZC702-CES-G

ZYNQ-7000 EPP ZC702 EVAL KIT

EL1848IYZ-T7

IC LED DRIVR WHITE BCKLGT 8-MSOP

EL7156CSZ

IC DRIVER PIN 40MHZ 3STATE 8SOIC

EL7158ISZ

IC DVR PIN 40MHZ 3STATE 8-SOIC

EL7222CSZ

IC DVR HS DUAL MOSFET 8-SOIC

EL7242CSZ

IC DVR HS DUAL MOSFET 8-SOIC

EL7243CMZ-T13

IC CCD DRIVER DUAL HS 20-SOIC

相关代理商/技术参数

EK-V7-VC707-CES-G

功能描述:VIRTEX-7 VC707 EVAL KIT RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

EK-V7-VC707-CES-G-J

功能描述:VIRTEX-7 VC707 EVAL KIT JAPAN RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Virtex®-7 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

EK-V7-VC707-G

制造商:Xilinx 功能描述:VIRTEX-7 FPGA VC707 EVALUATION KIT - Boxed Product (Development Kits) 制造商:Xilinx 功能描述:KIT EVAL VIRTEX7 VC707 制造商:Xilinx 功能描述:VIRTEX-7 VC707 FPGA EVAL KIT

EK-V7-VC707-G-J

制造商:Xilinx 功能描述:KIT EVAL VIRTEX7 VC707 JAPAN

EKWF111

功能描述:WiFi/802.11开发工具 WF111 SDIO Eval kit

RoHS:否 制造商:Roving Networks 产品:Evaluation Boards 工具用于评估:RN-171 支持协议:802.11 b/g 频率:2.4 GHz 接口类型:UART 工作电源电压:2 V to 16 V

EKWT11-A

功能描述:蓝牙/802.15.1 开发工具 EKWT11-A

RoHS:否 制造商:Panasonic Electronic Components 产品:Bluetooth Evaluation Kit 工具用于评估:PAN1721 频率:2.4 GHz 接口类型:I2C 工作电源电压:2 V to 3.6 V

EKWT11-E

功能描述:蓝牙/802.15.1 开发工具 EKWT11-E

RoHS:否 制造商:Panasonic Electronic Components 产品:Bluetooth Evaluation Kit 工具用于评估:PAN1721 频率:2.4 GHz 接口类型:I2C 工作电源电压:2 V to 3.6 V

EKWT11i-A

功能描述:蓝牙/802.15.1 开发工具 WT11i A Eval Kit

RoHS:否 制造商:Panasonic Electronic Components 产品:Bluetooth Evaluation Kit 工具用于评估:PAN1721 频率:2.4 GHz 接口类型:I2C 工作电源电压:2 V to 3.6 V